# BRM1553D Hardware-Software Interface Document (HSID)

Mil-Std-1553 Bus Controller, Remote Terminal and Bus Monitor

**USER'S MANUAL FOR:**

BRM1553D IP Cores, OCTAVA<sup>™</sup> Family, Minuet<sup>™</sup> Family, Orchestra<sup>™</sup> Boards

January 2020 - Added IRIG 106 data to MON stack

#### Copyright 2020 by Sital Technology Ltd.

All rights reserved. No part of this document may be reproduced, stored in a retrieval system, or transmitted in any form, or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Sital Technology Ltd.

\* DDC<sup>®</sup> and MINI-ACE<sup>®</sup> are registered trademarks of Data Device Corporation, Bohemia, NY, USA. There is not any affiliation between Data Device Corporation and Sital Technology, Ltd.

#### TABLE OF CONTENTS

| 1    | INTRODU       | CTION                                        | 8  |

|------|---------------|----------------------------------------------|----|

|      | 1.1 Abo       | ut this manual                               | 8  |

|      | 1.2 Abo       | ut BRM1553D – Mil-Std-1553 Core              | 9  |

|      | 1.3 Sma       | artWiring                                    | 10 |

|      | 1.4 Buil      | t-In testing                                 | 11 |

|      | 1.5 Exte      | ernal Loopback test                          | 11 |

|      | 1.6 Opt       | ional IP Contents                            | 11 |

|      |               | / memory parity check option                 |    |

|      | 1.8 Terr      | ns used in this document                     | 13 |

| Part | I: Remote Ter | minal and Monitor Mode - BRM1553D-RTMT       | 14 |

| 2    | Remote T      | erminal and Monitor                          | 15 |

|      |               | c Functionality                              |    |

|      | 2.1.1         | RT and its Setup                             | 15 |

|      | 2.1.2         | Message Monitor and its Setup                |    |

|      | 2.1.2.1       | Message Monitor IRIG106 Extension            | 17 |

|      | 2.1.3         | Non MIL-STD-1553B settings                   |    |

|      | 2.2 Bloc      | k Diagram                                    |    |

|      | 2.2.1         | Decoder/Encoder                              |    |

|      | 2.2.2         | The RT State Machine                         |    |

|      | 2.2.3         | The MT State Machine                         |    |

|      | 2.3 soft      | ware Interface                               | 20 |

|      | 2.3.1         | General Description                          |    |

|      | 2.3.2         | Registers Operation                          |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.2       |                                              |    |

|      | 2.3.2.3       |                                              |    |

|      | 2.3.2.4       |                                              |    |

|      | 2.3.2.5       |                                              |    |

|      | 2.3.2.6       |                                              |    |

|      | 2.3.2.7       |                                              |    |

|      | 2.3.2.8       |                                              |    |

|      | 2.3.2.9       |                                              |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.1       |                                              | 33 |

|      | 2.3.2.1       | 5                                            |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.1       |                                              |    |

|      | 2.3.2.2       |                                              |    |

|      | 2.3.2.2       |                                              |    |

|      | 2.3.2.2       | · · · · · · · · · · · · · · · · · · ·        |    |

|      | 2.3.2.2       |                                              |    |

|      | 2.3.2.2       |                                              |    |

|      | 2.3.2.2       |                                              |    |

|      | 2.3.3         | Memory Data Structure and Modes of Operation |    |

|      | 2.3.3         |                                              |    |

|      | 2.3.3.1       |                                              |    |

|      | 2.3.3.2       |                                              | 39 |

|      | 2.5.5.5       |                                              | 55 |

| BRM1553D – Hardware-Software Interface Document   | June, 2020 |

|---------------------------------------------------|------------|

| BRIVITSSSD – Haruware-Software Interface Document | June, 2020 |

| 2.3.3.4               | Stack contents                                       | 41 |

|-----------------------|------------------------------------------------------|----|

| 2.3.3.5               |                                                      | 42 |

| 2.3.3.6               | Mode Commands Interrupt Enable Lookup table          |    |

| 2.3.3.7               | Sub-address Lookup Table                             |    |

| 2.3.3.8               | Sub-address Control Word                             |    |

| 2.3.4                 | Memory management modes:                             |    |

| 2.3.5                 | Illegalization look up table                         |    |

| 2.3.6                 | Message Monitor look up table                        |    |

| 2.3.7                 | Single Transmit Message Mode                         |    |

| 2.3.8                 | Single Receive Message Mode                          |    |

| 2.3.9                 | Receive Double Buffering Message Mode                |    |

| 2.3.10                | Circular Buffer Message Mode                         | 53 |

| 2.3.11                | Global Circular Buffer Message Mode                  |    |

| 2.3.12                | Busy bit and condition                               |    |

| Part II: Legacy Bus ( | Controller Mode - BRM1553D-BC                        |    |

| 3 Bus Contro          | ller Introduction                                    |    |

| 3.1 Over              | view                                                 | 57 |

| 3.1.1                 | Non MIL-STD-1553B settings                           | 57 |

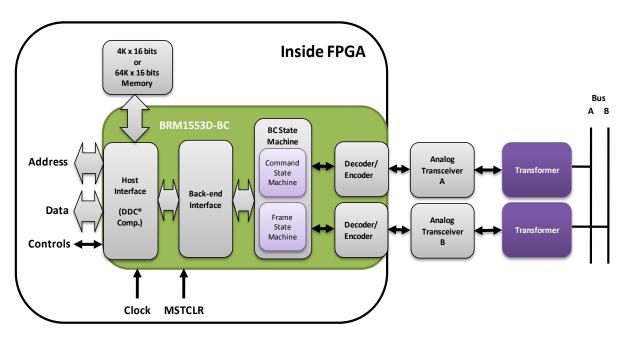

| 3.2 Block             | Diagram                                              | 58 |

| 3.2.1                 | The State Machines                                   | 58 |

| 3.3 Bus 0             | Controller Operation Modes                           |    |

| 3.3.1                 | Base Operation                                       | 60 |

| 3.3.2                 | Multi Frame Setup                                    | 60 |

| 3.3.3                 | Auto-repeat mode                                     | 60 |

| 3.3.4                 | Multi-frame & Auto-repeat                            | 61 |

| 3.3.5                 | Retry                                                | 61 |

| 3.3.6                 | Stop on error                                        | 62 |

| 3.3.7                 | Stop on status bits                                  | 62 |

| 4 BC Program          | nming and Setup                                      | 63 |

|                       | sters                                                |    |

|                       | ters Map                                             |    |

|                       | ter's Short Form Look Up Table                       | 65 |

| 4.3.1                 | Interrupt enable register #1 Address 0x0             |    |

| 4.3.2                 | Configuration Register #1 Address 0x1                |    |

| 4.3.3                 | Configuration Register #2 Address 0x2                |    |

| 4.3.4                 | Start Reset Register Writing to Address 0x3          |    |

| 4.3.5                 | Stack Pointer Register Reading from Address 0x3      |    |

| 4.3.6                 | Current BC control word. Address 0x4                 | 69 |

| 4.3.7                 | Time Tag Register – Address 0x5                      | 70 |

| 4.3.8                 | Interrupt Status Register #1 address 0x6             |    |

| 4.3.9                 | Configuration Register #3 address 0x7                |    |

| 4.3.10                | Configuration Register #4 address 0x8                | 73 |

| 4.3.11                | Configuration Register #5 address 0x9                |    |

| 4.3.12                | BC Frame Timing Remaining address 0xB                |    |

| 4.3.13                | BC Message Timing Remaining address 0xC              |    |

| 4.3.14                | BC frame time register address 0xD                   |    |

| 4.3.15                | BC Encoder test register 0x11                        |    |

| 4.3.16                | Passive TDR Level 0x12                               |    |

| 4.3.17                | Constant Value 0x13                                  |    |

| 4.3.18                | latched time tag register 0x15                       |    |

| 4.3.19                | Configuration Register #6 address 0x18               |    |

| 4.3.20                | Configuration Register #7 address 0x19               |    |

| 4.3.21                | Version of Core Register address 0x1A                |    |

| 4.3.22                | BC Condition code reading from register address 0x1B |    |

| 4.3.23                | Self Test Status register 0x1C                       |    |

| 4.3.24                | interrupt mask register #2 0x1d                      |    |

| 4.3.24                |                                                      |    |

| ΤΕСΗΝΟ             | BRM1553D – Hardware-Software Interface Document | June, 2020 |

|--------------------|-------------------------------------------------|------------|

| 4.3.25             | interrupt status register #2 0x1E               | 7          |

| 4.4 Me             | mory                                            |            |

| 4.4.1              | Memory Mapping                                  | 7          |

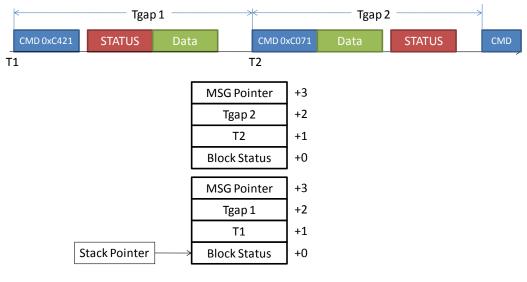

| 4.4.2              | Stack contents                                  |            |

| 4.4.3              | The Message Block                               |            |

| 4.4.4              | The BC Control word                             |            |

| rt III: Enhanced   | Bus Controller Mode - (eBC)                     | 8          |

|                    | d Bus Controller                                |            |

|                    | roduction                                       |            |

| 5.1.1              | Non MIL-STD-1553B settings                      |            |

|                    | s Controller operation modes                    |            |

| 5.2.1              | Basic operation                                 |            |

|                    | pgramming and Setup                             |            |

| 5.3.1              | Registers                                       |            |

| 5.3.1.1            |                                                 |            |

| 5.3.1.2            |                                                 |            |

| 5.3.1.3            |                                                 |            |

| 5.3.1.4            |                                                 |            |

| 5.3.1.             |                                                 |            |

| 5.3.1.6            |                                                 |            |

| 5.3.1.             |                                                 |            |

| 5.3.1.8            |                                                 |            |

| 5.3.1.9            |                                                 |            |

| 5.3.1.             |                                                 |            |

|                    |                                                 |            |

| 5.3.1.1<br>5.3.1.1 | · · · · · · · · · · · · · · · · · · ·           | و<br>و     |

|                    | · · · · · · · · · · · · · · · · · · ·           |            |

| 5.3.1.1            |                                                 |            |

| 5.3.1.1            |                                                 |            |

| 5.3.1.1            | •                                               |            |

| 5.3.1.1            |                                                 |            |

| 5.3.1.1            |                                                 |            |

| 5.3.1.1            |                                                 |            |

| 5.3.1.2            | · · · · · · · · · · · · · · · · · · ·           |            |

| 5.3.1.2            | · · · · · · · · · · · · · · · · · · ·           |            |

| 5.3.1.2            | 0                                               |            |

| 5.3.1.2            |                                                 |            |

| 5.3.1.2            | · · · · · · · · · · · · · · · · · · ·           |            |

| 5.3.1.2            | 0                                               |            |

| 5.3.1.2            |                                                 |            |

| 5.3.1.2            |                                                 |            |

| 5.3.1.2            |                                                 |            |

|                    | emory                                           | 10         |

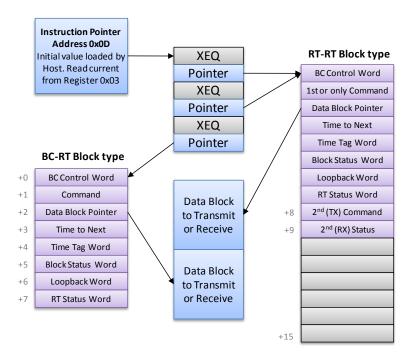

| 5.4.1              | Message Sequence Control                        |            |

| 5.4.2              | Variables                                       | 10         |

| 5.4.3              | Instructions                                    |            |

| 5.4.3.3            | 1 Data Condition Instructions                   | 10         |

| 5.4.4              | Message Block                                   |            |

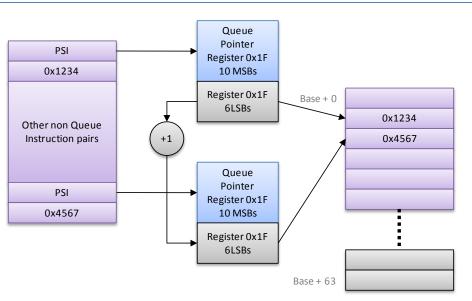

| 5.4.5              | General Purpose Queue                           |            |

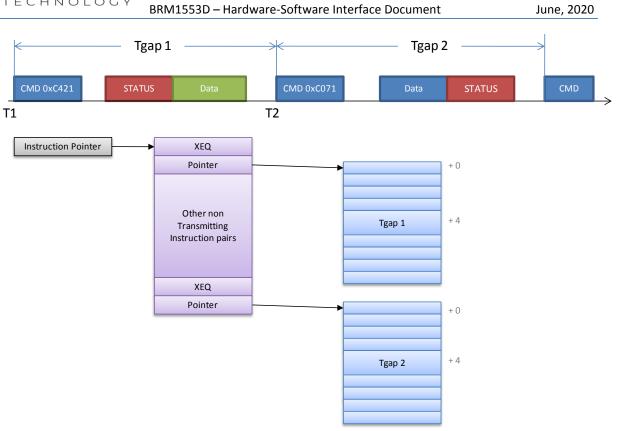

| 5.4.6              | Minor-Major message gap control                 | 11         |

| rt IV: Other Mo    | des                                             | 11         |

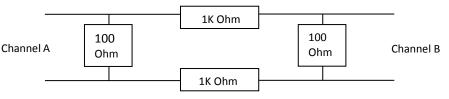

| 6 External         | Loop-back                                       | 11         |

| rt V: Extended     | Bit Rate - EBR1553 Option                       | 11         |

| 7 EBR Opti         | on                                              | 11         |

| 7.1 Int            | roduction                                       | 11         |

| ТЕСН     | NOLOGY BRM1553D – Hardware-Software Interface Document | June, 2020 |  |

|----------|--------------------------------------------------------|------------|--|

| 7.2      | EBR1553 Noise Rejection                                | 120        |  |

| 7.3      | EBR1553 added pins                                     |            |  |

| 7.4      | BC Mode and its Hub                                    |            |  |

| 7.5      | RT Mode                                                |            |  |

| 7.6      | MT Mode                                                |            |  |

| 7.7      | RT / MON Mode                                          |            |  |

| 7.8      | External Loopback                                      |            |  |

| 8 CyB    | BER Attack DETECTION Option                            |            |  |

| 8.1      | Introduction                                           | 123        |  |

| 8.2      | Cyber Report Signals                                   | 123        |  |

| Appendix | A: Changes tracking                                    |            |  |

| Appendix | B: INITIAL IP REGISTERS AND MEMORY VALUES              |            |  |

| Appendix | c: Pseudo code for simple BC transmission              |            |  |

| Appendix | Appendix D: Pseudo code for simple RT                  |            |  |

#### TABLE OF FIGURES

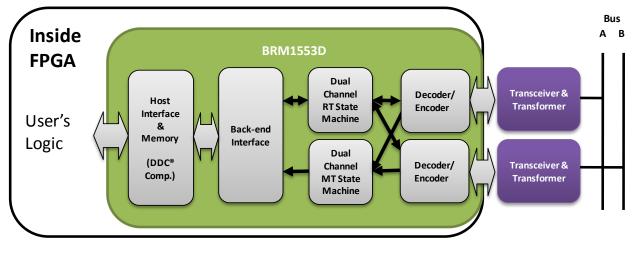

| Figure 1:  | BRM1553D-RTMT Block Diagram                       |     |

|------------|---------------------------------------------------|-----|

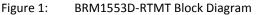

| Figure 2:  | Stuck Filling Up                                  |     |

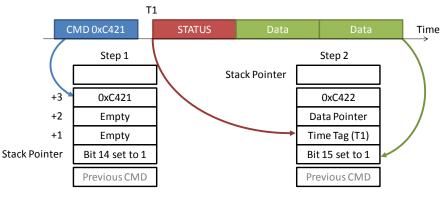

| Figure 3:  | Message Monitor lookup table                      |     |

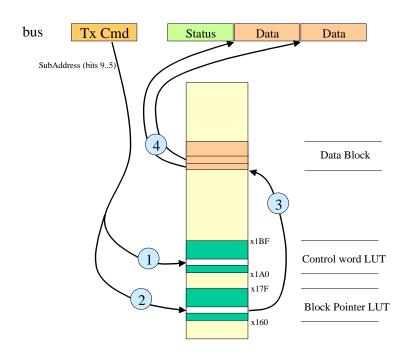

| Figure 4:  | Single Message mode transmit command              |     |

| Figure 5:  | Single message mode transmit command              |     |

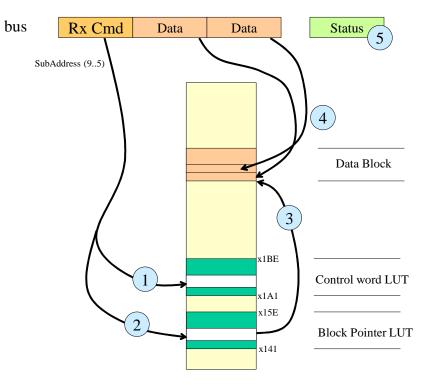

| Figure 6:  | Receive Double Buffering Message Mode             |     |

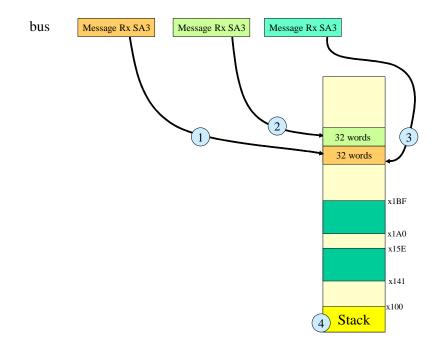

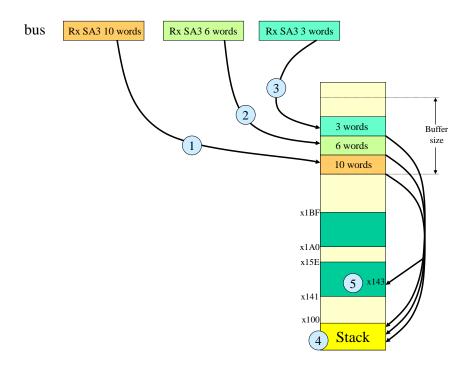

| Figure 7:  | Circular Buffer Message Mode                      |     |

| Figure 8:  | BRM1553D-BC Block Diagram                         |     |

| Figure 9:  | 3 <sup>rd</sup> Word Gap Time                     |     |

| Figure 10: | Execute BC sequencing                             | 101 |

| Figure 11: | General purpose Queue                             |     |

| Figure 12: | 4 <sup>th</sup> word example time-to-next-message | 113 |

| Figure 13: | Resistors Network for Loop-Back                   | 115 |

# **1 INTRODUCTION**

## 1.1 ABOUT THIS MANUAL

This document is the user's manual for BRM1553D, core for Sital's Mil-Std-1553 products. It covers the software interface – modes of operation, memory structure and registers operation – for Bus Controller (BC), Enhanced Bus Controller (eBC), Remote Terminal (RT) and Monitor (MT) parts of the core.

This manual is applicable for various Sital products, including Sital's IP Cores for FPGA, OCTAVA<sup>™</sup> and Minuet<sup>™</sup> components and Sital's board products.

#### This manual does not cover the hardware interface for these products.

The hardware interface of each product (IP cores, components, boards and other products from Sital) is covered under each product's Hardware Interface Manual.

In order to reduce the complexity of this manual, each part is covered in a different section. Some software registers and bits are used in a different manner between the various modes. It is assumed that if a user requires Bus Controller mode, for example, then it is not relevant to cover the functionality of a Remote Terminal mode in the same chapter, although it may be using the same set of registers and memory.

Therefore, the RT and MT Modes are covered in Part I, Legacy Bus Controller mode is covered on Part II, and Enhanced BC Mode is covered in Part III.

In some configurations of the core, depending on your product, the BC, RT and MT are packed together as a single IP core (BRM1553D-BCRTMT) or product. All reference made for BRM1553D-RTMT is equal to BRM1553D-BCRTMT, when in RT & MT Mode, and all reference made for BRM1553D-BC is equal to BRM1553D-BCRTMT, when in BC Mode.

#### 💷 <u>Note:</u>

The registers and memory mappings and functionality for this BRM1553D IP are defined to be as close as possible to those definitions as in DDC<sup>®</sup> Mini-ACE<sup>®</sup> and DDC<sup>®</sup> Enhanced Mini-ACE<sup>®</sup> devices, but the actual behavior of this BRM1553D IP is defined in this HSID specification and not in any other specification.

# 1.2 ABOUT BRM1553D - MIL-STD-1553 CORE

The BRM1553D core is used in various Sital products, including Sital's IP Cores for FPGA, OCTAVA<sup>™</sup> and Minuet<sup>™</sup> components and Sital's board products. This core provides a simple to use link for the MIL-STD-1553B Notice 2 bus interface.

The core supports all modes of Bus Controller (BC), Enhanced Bus Controller (eBC), Remote Terminal (RT), Message Monitor and Word Monitor (MT).

The BRM1553D as a stand-alone core was validated to meet the MIL-STD-1553B Notice 2 Remote Terminal Validation test plan, thus reliving the user from mastering the standard.

The BRM1553D IP was developed with state machine approach and does not include any micro code, thus all configuration register values are constantly available inside the hardware. This allows the configuration setup procedure to be performed in any order. Obviously, the go command when relevant should be the last command.

The BRM1553D IP was developed in vendor independent VHDL supporting all FPGA vendors and families of FPGA in a wide and flexible form. All Validation testing test benches in VHDL were also developed to support the safe addition of features and capabilities over time.

The VHDL IP has a few generic parameters that are set by Sital Technology during synthesis and are based on the mode of operations and various characteristics of the desired configuration. The customer must select the following parameters:

- 1. If to include the message monitor.

- 2. If to include the bus controllers.

- 3. The clock frequency of the IP.

- 4. If to support MIL-STD-1760, or not.

5. The level of Sital Smart Wiring, if to only detect a wiring fault, or also to locate it.

The IP is synthesized and delivered based on these parameters in VHDL gate level format. This unique delivery mode is also VHDL vendor independent gate level description of the IP implementing the above parameters. This makes the IP future prof and allows future retargeting of the netlist to newer FPGA families.

## 1.3 SMARTWIRING

Sital technology introduced a capability to the BRM1553D IP that detects and locates wiring failures of the 1553 bus connected with this IP.

The capability provided is a fully passive sensing circuit that constantly tracks the dynamic impedance along the wires to which this IP connects. This capability is fully implemented inside the IP, and does not require any external electronic circuits.

At a base level, if enabled, SmartWiring indicates to the Host CPU a single bit in one of the status reports, that there was a wiring fault, by means of setting a single bit on. The bit is set for the block status words of the BC, MT and RT.

At a higher level, if enabled, SmartWiring detection is provided to the BIT word in RT, supporting system level detection of wiring issue and report.

Yet at a higher level, if enabled, SmartWiring data base of 128 words is provided to the Host, allowing additional analysis and pin pointing the location of the wiring fault in the system.

SmartWiring is enabled during IP generation in a number of levels. First level is to report to the local Host through interrupt status register 1 bit 14, second level would set bit 12 in BIT register, thus supporting system level report in RT mode, and a third level would allow location analysis by accessing registers from address 128 to 255.

SmartWiring\_Clock is an input to the IP, and should be a multiple of the main clock in the range of 100Mhz to 200Mhz.

#### 💿 <u>Note:</u>

The Smart Wiring data base is mapped to the registers address space. It is mapped from address 32 (0x20) to address 127 (0x7F).

This is specifically required in case more than 1 IP is mapped in the address space, such as with a 4 channel 1553 IP.

## 1.4 BUILT-IN TESTING

The mini-ACE devices developed by DDC were assembled from a few ASIC chips in a hybrid package. In order to reduce risk of hybrid wiring disconnections, DDC included a few built-in tests to verify that these connections are intact.

These tests cover all hybrid traces, but obviously not all internal ASIC chips traces.

Some tests have been executed automatically during power-up, such as protocol test, and a pass fail report was issued within 2 ms of power-up.

Some additional tests, which are not built in, that cover board level traces have been executed by the EMA API and the host CPU.

The Sital Technology BRM1553D IP is holey implemented in one FPGA ASIC fabric and thus do not require execution of such built-in tests. Thus the IP is not muted for 2 ms at power-up to perform these built-in tests. However, some user programs rely on the successful pass of the test, and ping for its success as part of the device power-up sequence.

For these backward compatibility reasons, the BRM1553D IP emulates the tests result report and indicates successful pass in <u>register 0x1C</u> as if the tests were executed.

It is highly recommended to perform power-up testing to the IP from the host side. These tests should cover the PCB traces between the IP and the host CPU. These may include the address-data bus lines, the interrupt line if used, the RT-Address lines if testable, and transceiver-transformer connections if testable, and any other relevant PCB traces.

## 1.5 EXTERNAL LOOPBACK TEST

The BRM1553D IP supports the loopback testing, either internally or externally between bus A and B. Please refer to <u>chapter 6</u> for details.

#### 1.6 OPTIONAL IP CONTENTS

The IP was enriched with additional features that are added to the IP by control Generic Options during synthesis. These generic options are a vector of bits where each bit indicates the availability of that capability in the generated netlist. The vector of bits can be read from Register 0x15 reset value. After reset, these bits are overwritten with Register 0x15 functional values.

Bit  $0 \Rightarrow '1'$  - Add micro instructions to enhanced BC to Jump on Data value as in GE FANUC BC.

- Bit  $1 \Rightarrow 1' 16$  MSBs of Time Tag in address 0x15. 0' Register 0x15 latches register 0x5.

- Bit 2 => '1' Add memory parity error checking.

- Bit  $3 \Rightarrow '1' Add$  Busy LUT for each Sub Address as in DDC EMA.

- Bit 4 => '1' Add IRIG106 Chapter 10: External 48 Time Tag & RTs Response time into Data Monitor Tail

# 1.7 RAM MEMORY PARITY CHECK OPTION

There is a synthesis option for memory parity check in the BRM1553D.

If the enhanced mode is enabled and configuration register 2 bit 14 is set high, then Parity is checked. When reading a non-initialized RAM entry by the IP or the CPU, or if Parity error is detected during the operation, bit 14 of the interrupt status word 1 is set.

For the BRM1553SPI IP, when doing an SPI read access, the SPI slave inside this IP pre-fetches an additional word that is not sent to the host. If this word was not Parity initialized (by writing to that address), then A RAM Parity error might Occur. Best practice would be to initially write the full length of the RAM, and that should set the parity right for the entire RAM.

## 1.8 TERMS USED IN THIS DOCUMENT

- **Remote Terminal (RT)** The part of the FPGA that manages the 1553 communications and implemented by the core.

- **Bus Controller (BC)** the system that handles Mil-Std-1553 timing and manages the transmission of RT's on the bus.

- **eBC** Enhanced Bus controller.

- **SubSystem** The whole box that connects to the MIL-STD-1553 bus that contains the FPGA part of it is the Remote Terminal.

- Host the CPU running the SubSystem and managing the IP core interface.

- **FPGA** Programmable device that contains the BRM1553D RT & MT MODE core and user logic and is part of the Subsystem.

- User Logic Logic Circuit that resides in the FPGA that is not the BRM1553D RT & MT MODE core and connects to it.

- **Message** the group of command data and status words that compose a 1553 message.

- IP Intellectual Property

- **Core** Supplied logic circuit that interfaces to MIL-STD-1553 bus.

- ICD Interface Control Document.

- TA Terminal Address of the command / status words. Bits 11 to 15.

- SA Sub Address of the command word. Bits 5 to 9.

- WC Word count field of command. Bits 0 to 4.

- **Muxbus** Time multiplexed bus known as the MIL-STD-1553B Notice 2 bus.

- **SW** software.

- **BCST** Broadcast command.

- **TX** Transmit.

- **RX** Receive.

- **SACW** The Sub-address control word.

- LUT Look Up Table.

- When a reference is made to a particular register and a specific bit, the notation is R01B12 for Register address 0x0001 and bit 12.

- When a reference is made to a particular memory location, the notation is M0100 for memory address 0x0100.

- Referencing Configuration register #3, bit 5 is '1' as CR3/5=1

- SmartWiring the capability to sense wiring problems of bus connected to this IP.

# PART I: REMOTE TERMINAL AND MONITOR MODE -BRM1553D-RTMT

# 2 REMOTE TERMINAL AND MONITOR

## 2.1 BASIC FUNCTIONALITY

#### 2.1.1 RT AND ITS SETUP

A Remote Terminal allows a subsystem to send and receive data to and from a Mil-Std-1553 bus. The communication is controlled by a Bus Controller (BC). A single BC controls the communications with up to 31 RTs, in accordance with its On Flight Program (OFP). An RT can never initiate any communication – receive or transmit data – without a direct command from a BC.

In some configurations it is demanded that BC Mode will be disabled by hardware in order to prevent accidental transmission of data to the bus.

The BRD1553D will power up in BC or IDLE mode. If 1760 mode is enabled (in some versions) the BRM1553D will power up in RT busy mode, as required by the Mil-Std-1760 standard. During the busy period, the RT will reply with the busy bit set in its status responses if it was assigned a valid RT Address. In this mode no data is sent and data received from the bus controller is dumped.

During the busy period, the software should setup all registers and memory locations that are needed for proper functionality of the core.

Once the setup of all registers and memory mappings is done, the busy bit can be reset (by writing to configuration register 1) and from that point on the core will start responding to 1553 bus commands.

The dual port shared memory array is reset on power-up. However the "Reset" signal does not reset the memories inside the core. If Reset is applied from the user logic, all registers in the core are reset.

The BRM1553D supports the Message Monitor mode, and this mode could be enabled concurrently to the RT running. Please refer to the next section for a description on the Message Monitor mode.

#### 2.1.2 MESSAGE MONITOR AND ITS SETUP

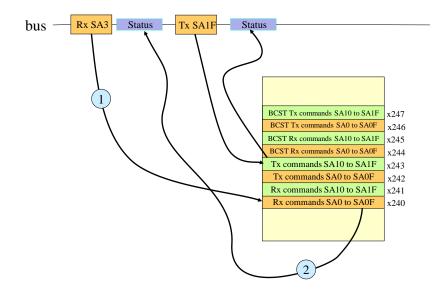

The Message Monitor (MM) mode allows for recording selected messages from 1553 bus into the memory. The software defines a lookup table in memory where each bit enables the recording of a message with a specific Terminal Address, transmit or receive bit and a specific sub-address.

Message Monitor is useful in various ways. The simple usage is during flight when a Remote Terminal requires pieces of data from the ICD that is not sent directly to it, but rather to another Terminal. This mode reduces the amount of data on the bus, or allows adding features to a terminal without changing the ICD (changing the OFP software).

A second common usage is for recording purposes onto a recording media, and the ability to analyze the transactions on the Muxbus after flight.

The MM can operate as standalone, or concurrently with the RT.

#### BRM1553D – Hardware-Software Interface Document

The MM can be stopped and enabled during the operation of the device.

If the MM is enabled in the RT concurrent monitor mode then the MM will start monitoring after setting this mode to 'on'.

If the MM is operating as standalone, it will start recording transportation only after an MT start command.

In both modes, the MM can be stopped and started by the software.

When stopped or started, the 'on' and 'off' state will not hurt a currently running message.

The MM records all messages regardless of the RT operating or not. Messages meant for the concurrent RT are recorded if the appropriate 'enable' bits are set high.

Monitor setup involves programming the relevant configuration registers as well as setting up several memory addresses in the shared memory space.

Please refer to the register description and memory mapping locations to program the relevant memory locations.

The registers that need to be addressed are:

- Configuration register #3 to setup command and data stack sizes.

- Memory locations 0x0102 and 0x0103 for initial pointers.

- Selective monitor lists from Memory address 0x0280.

- Configuration register #1 to enable the Message monitor mode.

Optional:

- Reset register 0x03 bit 1 to starts the recording in standalone mode.

- MT Stop by writing 1 to bit 6 of Reset register 0x03.

Sital Unique mode: configuration register 6, bit 3 if set to '1' In Message Monitor only mode, the time tag is reset or updated based on selectively recorded mode messages. Only valid messages will load the time tag.

Special note on Area A to Area B change during standalone MM: In order to change the memory stack pointers area during monitoring, it is required to access configuration register 1 bit 13. However, all bits are accessed during this write. When accessing configuration register #1 the mode of operation is determined, and thus a start command must follow the area change write.

#### 2.1.2.1 MESSAGE MONITOR IRIG106 EXTENSION

As of version 011A (January 1<sup>st</sup> 2020), the message monitor command stack added a new mode of operation, with 8 words instead of 4 if the BRM1553D IRIG106 mode of operation is enabled. The added 4 words hold the 48 time tag of the message and the RT response time during that message.

This is a critical change since the command stack increments by 8 not by 4 as in Enhanced Mini ACE. The total amount of messages that can be stored in the command stack is halved.

In order to enable this mode of operation, please set configuration register #7 bit 8 to '1'.

#### 2.1.3 NON MIL-STD-1553B SETTINGS

The IP core is set to support different dialects than 1553B, by means of configuration.

These different settings affect both the RT and Message Monitor modes. The BC and eBC are also affected, please refer to the appropriate section.

The configuration register 3 bit 1, when set high, sets SA 31 to be non-mode, but rather a regular SA. In addition, this setting will assume only mode commands without data, so the RT will not reply, nor accept data words for messages designated to it with SA=0.

When this bit is set, both transmit last command and transmit status mode codes will not retain the status bits as they do in 1553B, but rather treat as any other mode command and clear the status bits for the reply.

Using configuration register #3 bit 5 set high, it is possible to manage all 11 LSBs of the RT status reply, including the ME bit. In 1553A, the RT responds to a valid command with invalid data words with a status word and ME set. In 1553A only bits 10 and 0 are meaningful. The RT when set to 1553A mode, will follow this behavior and respond with ME in status word, but if the host wants to set ME as well, it is possible through this configuration and settings.

Using Configuration register 5 bit 7, it is possible to turn Broadcast address 31 to a standard RT as defined by 1553A.

The RT response time was shortened to be slightly less than 7 us (5 us dead time) in order to support both 1553A and 1553B.

# 2.2 BLOCK DIAGRAM

# 2.2.1 DECODER/ENCODER

The BRM1553D-RTMT core incorporates two decoders that translate the serial bus messages from the MIL-STD-1553 Manchester coding and format, into a 16 bit parallel data accompanied by status indications for each word. Two concurrently operated state machines, the RT state machine, and the MT state machines, analyze these words.

There are two identical blocks of Decoder/Encoder, in order to accommodate the dual-redundancy required by the Mil-Std-1553 standard.

## 2.2.2 THE RT STATE MACHINE

The RT state machine identifies a set of these bus words as a valid message, being 'transmit', 'receive', 'mode' or 'broadcast' message. When the RT State Machine decides it has to either store a word to the subsystem or fetch a word from the subsystem it interfaces through the backend to the internal memory array, and stores or reads that word.

When transmitting words, a word is fetched from the host interface by the back-end logic, and is loaded into the encoder by the Dual channel RT state machine. The encoder formats the words into serial Manchester 2 coding and emits them to the 1553 transceivers and onto bus A or B.

## 2.2.3 THE MT STATE MACHINE

The Dual channel Monitor state machine searches for valid commands. When a command is found, the state machine checks whether this command defines a message required for monitoring. In such case, the state machine manages the process of storing the words one by one in the interface memory into a pre-defined location.

The words received and transmitted are arranged in a dual port memory according to the memory mapping of the enhanced mini-ACE remote terminal. The BRM1553D-RTMT implements all memory modes of operations as will describe in the following sections.

## 2.3 SOFTWARE INTERFACE

#### 2.3.1 GENERAL DESCRIPTION

The interface to the device is divided between several control registers and memory access. The registers are used to control the device and its operation, while the memory is used as the 1553 message interface and control.

The registers are mapped to address 0x0 to 0x20 and can be written or read (depending on their functionality). Memory can be in different size, depending on the device and ordered configuration. The IP core can be set between 2K, 4K, 8K, 16K, 32K or 64K – all by 16 bits, OCTAVA devices can be either 4K or 64K by 16 bits and Minuet devices can be 8K or 16K words. Sital boards vary between 8K to 64K Words RAM per channel. Please see the applicable hardware interface document for the specific memory configuration for your device.

Access to the registers or memory is done through the same address and data lines, however, in the IP core products and components, when accessing the registers, the MEM\_nREG signal should be kept low, and when accessing the memory this signal should be high. At Sital's 1553 boards, the driver should set two different address blocks to distinguish between memory and registers.

There are several dependencies between the configuration of registers and the configuration and operation of the memory. The user must verify that all dependencies configured correctly with accordance to the required operation of the device.

#### 2.3.2 REGISTERS OPERATION

The software interface of the core to the host processor consists of 20 internal operational registers for normal operation. These registers determine the device configuration, modes of operation, memory structure, interrupt control and status, etc.

The address mapping for the registers is detailed in the following table:

#### 💷 <u>Note:</u>

If a bit is defined as read only, then the core acts according to the specified level, and the read operation is available for software compatibility to existing code. However, these bits may be written with values which will be ignored by the core.

If the bit is Write/Read, then the default value is as defined but could be changed to desired level for the required operation.

| Address |    | Add | lress Li | nes |    | Register Description (Read/Write)                                                   |

|---------|----|-----|----------|-----|----|-------------------------------------------------------------------------------------|

|         | A4 | A3  | A2       | A1  | A0 |                                                                                     |

| 0x0     | 0  | 0   | 0        | 0   | 0  | Interrupt Mask Register #1 (RD/WR)                                                  |

| 0x1     | 0  | 0   | 0        | 0   | 1  | Configuration Register #1 (RD/WR)                                                   |

| 0x2     | 0  | 0   | 0        | 1   | 0  | Configuration Register #2 (RD/WR)                                                   |

| 0x3     | 0  | 0   | 0        | 1   | 1  | Start/Reset Register (WR)                                                           |

| 0x3     | 0  | 0   | 0        | 1   | 1  | RT Command Stack Pointer (RD)                                                       |

| 0x4     | 0  | 0   | 1        | 0   | 0  | RT Subaddress Control Word Register (RD)                                            |

| 0x5     | 0  | 0   | 1        | 0   | 1  | Time Tag Register (RD/WR)                                                           |

| 0x6     | 0  | 0   | 1        | 1   | 0  | Interrupt Status Register #1(RD)                                                    |

| 0x7     | 0  | 0   | 1        | 1   | 1  | Configuration Register #3 (RD/WR)                                                   |

| 0x8     | 0  | 1   | 0        | 0   | 0  | Configuration Register #4 (RD/WR)                                                   |

| 0x9     | 0  | 1   | 0        | 0   | 1  | Configuration Register #5 (RD/WR)                                                   |

| 0xA     | 0  | 1   | 0        | 1   | 0  | (RD) – all 'O'                                                                      |

| 0xB     | 0  | 1   | 0        | 1   | 1  | Not relevant for RT – see BC mode manual for details                                |

| 0xC     | 0  | 1   | 1        | 0   | 0  | Not relevant for RT – see BC mode manual for details                                |

| 0xD     | 0  | 1   | 1        | 0   | 1  | RT Last Command (RD)                                                                |

| 0xE     | 0  | 1   | 1        | 1   | 0  | RT Status Word Register (RD)                                                        |

| 0xF     | 0  | 1   | 1        | 1   | 1  | RT BIT Word Register (RD)                                                           |

| 0x10    | 1  | 0   | 0        | 0   | 0  | Not implemented                                                                     |

| 0x11    | 1  | 0   | 0        | 0   | 1  | Test register. Supports external loopback test in Word Monitor mode.<br>Requires BC |

| 0x12    | 1  | 0   | 0        | 1   | 0  | 0x3210                                                                              |

| 0x13    | 1  | 0   | 0        | 1   | 1  | 0x7654                                                                              |

| 0x14    | 1  | 0   | 1        | 0   | 0  | Not implemented                                                                     |

| 0x15    | 1  | 0   | 1        | 0   | 1  | Latched Time Tag Register                                                           |

| 0x16    | 1  | 0   | 1        | 1   | 0  | Not implemented                                                                     |

| 0x17    | 1  | 0   | 1        | 1   | 1  | Not implemented                                                                     |

| 0x18    | 1  | 1   | 0        | 0   | 0  | Configuration Register #6 (RD/WR)                                                   |

| 0x19    | 1  | 1   | 0        | 0   | 1  | Configuration Register #7 (RD/WR) – bit 5 is set by bit 9                           |

| 0x1A    | 1  | 1   | 0        | 1   | 0  | version of Core (RD)                                                                |

| 0x1B    | 1  | 1   | 0        | 1   | 1  | Not relevant for RT – see BC mode manual for details                                |

| 0x1C    | 1  | 1   | 1        | 0   | 0  | BIT Test Status Register (RD)                                                       |

| 0x1D    | 1  | 1   | 1        | 0   | 1  | Interrupt Mask Register #2 (RD/WR)                                                  |

| 0x1E    | 1  | 1   | 1        | 1   | 0  | Interrupt Status Register #2 (RD)                                                   |

| 0x1F    | 1  | 1   | 1        | 1   | 1  | Not relevant for RT – see BC mode manual for details                                |

#### 2.3.2.1 INTERRUPT MASK REGISTER #1 ADDRESS 0X0

If the Host enables one of the bits below to '1' and the specified event occurs, an interrupt will be generated to the Host CPU. There are three methods to clear the interrupts, please refer to <u>interrupt status register 1</u> for details. The status bits are set regardless of the masking bit.

| Bit # | Read/Write/Default | What event triggers the interrupt when enabled by '1'.                                                                                                                                                                                                  |

|-------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13    | R/W/'0'            | Transmitter timeout occurred. Timeout occurs when transmission is on for more than 768 us (660 us is the longest possible transmission).                                                                                                                |

| 12    | R/W/'0'            | RT Stack Rollover occurred. Occurs when a new message is written to the stack and its write address is the base of the stack.                                                                                                                           |

| 11    | R/W/'0'            | Monitor command stack rollover occurred. Occurs when a new message is written to the stack and its write address is the base of the stack.                                                                                                              |

| 10    | R/W/'0'            | Monitor data stack rollover occurred. Occurs when a new message is written to the stack and its write address is the base of the stack.                                                                                                                 |

| 9     | R/W/'0'            | Memory Handshake error - Not relevant for BRM1553D, always zero.                                                                                                                                                                                        |

| 7     | R/W/'0'            | RT Address parity error found. If selected RT address parity does not match the RT address parity bit.                                                                                                                                                  |

| 6     | R/W/'0'            | Time tag counter rollover. Is set high when the time tag counter rolls back from 0xFFFF to 0x0000.                                                                                                                                                      |

| 5     | R/W/'0'            | Enable interrupt for RT circular buffer modes ( <u>local</u> or <u>Global</u> ) rolled back to the buffer base.                                                                                                                                         |

| 4     | R/W/'0'            | End Of Message, if control word is enabled. Set high when the RT Sub Address LUT interrupt request bit is high, to indicate that a specific message has arrived.                                                                                        |

| 2     | R/W/'0'            | Transmitted words Loop back error, or Message Error in received words. This bit is set high if the echo bits of the transmission does not match the transmitted bits, or the RT responded with a message error (bit 10) of the status word set to high. |

| 1     | R/W/'0'            | Mode command received. This bit is set high upon arrival of a valid mode command.                                                                                                                                                                       |

| 0     | R/W/'0'            | EOM – End Of Message found. Set high following a successful completion of a valid message.                                                                                                                                                              |

All other bits are read only and read value is zero.

Optional for the core: all bits can be written and read, but only the specified bits have effect.

Default Value: 0x0000 – all events masked.

#### 2.3.2.2 CONFIGURATION REGISTER #1 ADDRESS 0X1

Configuration Register #1 starts in IDLE BC mode. In Mil-STD-1760 mode this register starts in RT busy mode. For this document it is assumed that RT or MT functions are initiated. For BC function details please refer to Part II: Bus Controller Mode.

RT without alternate status (configuration register #3 bit 5 = '0') is bits:

| Bit # | Read/Write/Default   | Description                                                                                                                                                                                                                                                                                                                   |

|-------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | R/W/'0'              | <ul> <li>'1' For Enhanced RT.</li> <li>A hardware input 'M1760' (if exists on the IP core) when set high before HW reset cycle is complete, powers up to RT + Busy for MIL-STD-1760 compatibility.</li> <li>'0' For legacy BC. In this case some of the other registers and bits have different meaning and usage.</li> </ul> |

| 14    | R/W/'0'              | '1' for Message Monitor <b>Only</b> function. If bit 15 is high (RT) this bit should be '0' and bit 12 enables MT.                                                                                                                                                                                                            |

| 13    | R/W/'0'              | <ul> <li>'1' area B. Fixed memory locations =&gt; 0x0104, 0x0105</li> <li>'0' area A. Fixed memory locations =&gt; 0x0100, 0x0101</li> <li>Area Change will take place after message has ended.</li> <li>The read value is the actual area used.</li> </ul>                                                                   |

| 12    | R/W/'0'              | <ul><li>'1' Message Monitor Enable.</li><li>'0' Message Monitor Disabled.</li></ul>                                                                                                                                                                                                                                           |

| 11    | R/W/'0'<br>Assumed 1 | Dynamic bus control bit. This BRM1553D does not allow to set Dynamic bus acceptance bit in status word, regardless of this bit value!                                                                                                                                                                                         |

| 10    | R/W/'0'              | Busy bit. If '0' is written, Busy bit and busy state of the RT is engaged. No words will be sent by the RT in response to commands only status word with busy bit set to '1'.                                                                                                                                                 |

| 9     | R/W/'0'              | Service Request bit. If '0' is written, Service Request bit in status word is set to '1'.                                                                                                                                                                                                                                     |

| 8     | R/W/'0'              | Sub System Flag bit. If '0' is written, Sub System Flag bit in status word is set to '1'.                                                                                                                                                                                                                                     |

| 7     | R/W/'0'              | RT Flag bit. If '0' is written, RT Flag bit in status word is set to '1'.                                                                                                                                                                                                                                                     |

| 2     | Read/'0'             | <ul> <li>'1' – MT state machine has been started</li> <li>'0' – MT is idle. Before trigger on, or after trigger off, or just off.</li> </ul>                                                                                                                                                                                  |

| 0     | Read/'0'             | Message in Progress. Is set by the core to '1' on SOM and reset to '0' on EOM.                                                                                                                                                                                                                                                |

RT with alternate status (configuration register #3 bit 5 = '1' and enhanced mode (bit 15 = 1)) is bits:

| Bit # | Read/Write/Default | Description                                                                                                                                                                                                                                                  |

|-------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | R/W/'0'            | '1' For Enhanced RT.                                                                                                                                                                                                                                         |

| 14    | R/W/'0'            | 'O' for Enhanced RT.                                                                                                                                                                                                                                         |

| 13    | R*/W/'0'           | <ul> <li>'1' area B. Fixed memory locations =&gt; 0x0104, 0x0105</li> <li>'0' area A. Fixed memory locations =&gt; 0x0100, 0x0101</li> <li>Area Change will take place after message has ended.</li> <li>*The read value is the actual area used.</li> </ul> |

| 12    | R/W/'0'            | <ul><li>'1' Message Monitor Enable.</li><li>'0' Message Monitor Disabled.</li></ul>                                                                                                                                                                          |

| 11    | R/W/'0'            | A '1' on this bit sets RT status bit 10 to '1'. Message Error bit.                                                                                                                                                                                           |

| 10    | R/W/'0'            | A '1' on this bit sets RT status bit 9 to '1'. Instrumentation bit.                                                                                                                                                                                          |

| 9     | R/W/'0'            | A '1' on this bit sets RT status bit 8 to '1'. Service Request bit.                                                                                                                                                                                          |

| 4     | R/W/'0'            | A '1' on this bit sets RT status bit 3 to '1'. Busy bit.                                                                                                                                                                                                     |

BRM1553D – Hardware-Software Interface Document

June, 2020

| 3 | R/W/'0'  | A '1' on this bit sets RT status bit 2 to '1'. Subsystem flag bit.             |

|---|----------|--------------------------------------------------------------------------------|

| 1 | R/W/'0'  | A '1' on this bit sets RT status bit 0 to '1'. Terminal Flag bit.              |

| 0 | Read/'0' | Message in Progress. Is set by the core to '1' on SOM and reset to '0' on EOM. |

## 2.3.2.3 CONFIGURATION REGISTER #2 ADDRESS 0X2

| Bit # | Read/Write/Default | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | Assumed 1          | '1' – Enhanced Interrupts mode enabled.                                                                                                                                                                                                                                                                                                                                                                    |

| 14    | R/W/'0'            | '0' – No Memory Parity bit check.                                                                                                                                                                                                                                                                                                                                                                          |

|       |                    | '1' – Enable Memory Parity check. Optional feature.                                                                                                                                                                                                                                                                                                                                                        |

| 13    | R/W/'0'            | '1' – <u>Enable BUSY lookup table</u> . Requires CR3/15=1 to take effect.<br>This LUT is synthesis Optional. Default is off.                                                                                                                                                                                                                                                                               |

| 12    | R/W/'0'            | <ul><li>'0' – Double buffer for Rx messages is disabled.</li><li>'1' – Double buffer for Rx depends on bit 1 of this register.</li></ul>                                                                                                                                                                                                                                                                   |

| 11    | Assumed 1          | '1' – Overwrite Invalid data Enabled.                                                                                                                                                                                                                                                                                                                                                                      |

| 10    | Assumed 0          | '0' – Rollover at 256-word boundaries                                                                                                                                                                                                                                                                                                                                                                      |

| 97    | R/W/'000'          | Time Tag resolution*: Set these three bits to determine the time between<br>increments of the time tag (TTag) counter. The TTag is a 16 bit register<br>accessible through <u>register address 5</u> .<br>"000" - 64 usec, "001"- 32 usec, "010"- 16 usec,<br>"011" - 8 usec, "100"- 4 usec, "101"- 2 usec,<br>"110" - Increment each time a "1" is written to Start Reset Register address<br>0x03 bit 4. |

|       |                    | "111" – Increments on Rising edge of TAG_CLK.                                                                                                                                                                                                                                                                                                                                                              |

| 6     | R/W/'0'            | <ul> <li>'0' – Time Tag counter controlled by Host only.</li> <li>'1' – clears Time Tag counter when synchronize without data mode command is received.</li> </ul>                                                                                                                                                                                                                                         |

| 5     | R/W/'0'            | <ul> <li>'0' – Time Tag counter controlled by Host only.</li> <li>'1' – Loads Time Tag counter when synchronize with data mode command is received.</li> </ul>                                                                                                                                                                                                                                             |

| 4     | R/W/'0'            | <ul> <li>'1' – Auto clear of interrupt status registers #1 and #2 as a result of CPU reading their value. Clears only register read.</li> <li>'0' – clear by reset register 0x03 only.</li> </ul>                                                                                                                                                                                                          |

| 3     | R/W/'0'            | <ul> <li>'0' – generates a 500ns* low pulse on the INTn signal.</li> <li>'1' – Level mode. INTn stays low until the host reads status register(s).</li> </ul>                                                                                                                                                                                                                                              |

| 2     | R/W/'0'            | <ul> <li>'0' – Service Request Status bit only set by Host.</li> <li>'1' – Service request set by Host, is cleared by 1553 Transmit Vector Word mode command.</li> </ul>                                                                                                                                                                                                                                   |

| 1     | R/W/'0'            | <ul> <li>'0' – If bit 12 is '1', globally sets double buffer for all Rx commands. If bit 12 is '0', globally sets single buffer.</li> <li>'1' – Each SA can have different buffering mode depending on sub-address lookup table (see below).</li> </ul>                                                                                                                                                    |

| 0     | R/W/'0'            | <ul> <li>'0' – BCST pointers are the same as Receive pointers.</li> <li>'1' – Separate BCST data pointers from receive data pointers can be defined<br/>in the sub-address LUT.</li> </ul>                                                                                                                                                                                                                 |

\*note: accuracy of timing is identical with the accuracy of the input clock to the IP.

#### 2.3.2.4 START RESET REGISTER WRITING TO ADDRESS 0X3

This is a write register for one purpose, reading back is the stack pointer value.

| Bit number | Read/<br>Write/<br>Default | Description                                                                                                                                                                                                                                                    |

|------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10         | Write                      | '1' clear self-test register at address 0x1C.                                                                                                                                                                                                                  |

| 9          | Write                      | '1' initiate RAM self-test.                                                                                                                                                                                                                                    |

| 7          | Write                      | '1' initiate Protocol self-test.                                                                                                                                                                                                                               |

| 6          | Write                      | '1' Stop the Message Monitor from recording.                                                                                                                                                                                                                   |

| 4          | Write                      | '1' Increments the Time Tag register if such mode set in configuration register #2.                                                                                                                                                                            |

| 3          | Write                      | '1' resets the Time Tag counter. The time tag counter is also controlled by<br>'Synchronize' and 'Synchronize with data mode' commands from the 1553 bus.                                                                                                      |

| 2          | Write                      | '1' resets the interrupt. Resets the FF that latches the interrupt condition. If the condition for interrupt persists, the relevant FF would be set again until the condition for causing this interrupt is cleared.<br>Reset of Interrupt Register #1 and #2. |

| 1          | Write                      | '1' Starts the Message Monitor (MM) after it was stopped by writing '1' to bit 6 or it is in the Message Monitor only mode. In RT/MM mode a start is not required.                                                                                             |

| 0          | Write                      | '1' Reset core. Reset all registers, FFs in core. Memories are not reset, and should be reset by CPU. If '1', all other bits have no effect.                                                                                                                   |

## 2.3.2.5 STACK POINTER REGISTER READING FROM ADDRESS 0X3

This is a read only register. Writing to it is explained above.

| Bit number | Read/<br>Default | Description                                                                                                                                                                                                                                             |

|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 150        | Read<br>Ox0      | Copy of the Stack pointer value.<br>After the EOM bit (15) is written to the first word of the stack entry, the stack<br>pointer is incremented by 4. This pointer value can either be read from the<br>memory in address 0x100, or from this register. |

#### 2.3.2.6 RT SUB-ADDRESS CONTROL WORD ADDRESS 0X4

Read back of the currently used RT Sub address control word.

#### 2.3.2.7 TIME TAG REGISTER READING FROM ADDRESS 0X5

The time tag counter can be reset by writing to this register the value 0x0 or be loaded to any other value by writing the value into this register.

The time tag counter counts in clock steps defined by configuration register #2.

The time tag counter is also managed by the 1553 bus controller by two mode commands:

- Synchronize without data, will reset this counter, and

- Synchronize with data, will load this counter to the value sent on the bus.

The counter will rollover every 2^16 \* resolution. Resolution is controlled by configuration register #2.

The value of this counter is also reset by the hardware raw\_reset line, or the software reset done by writing '1' to the LSB of the reset register.

The value of the time tag counter is placed in the stack of each newly arrived message. Please see "Stack contents" section for details.

Sital Unique Mode: For monitor only mode, if configuration register 6 bit 3 is set high, the time tag register is also updated by all RT time tag mode commands that are selected to be recorded.

| Bit number | Read/<br>Write/<br>Default | Description                                                              |

|------------|----------------------------|--------------------------------------------------------------------------|

| 150        | R/W/'0'                    | Read the Time Tag Counter.<br>Write a new value to the time tag counter. |

#### 2.3.2.8 INTERRUPT STATUS REGISTER #1 ADDRESS 0X6

This register indicates the cause of an interrupt.

The status bits will be cleared as a result of either of:

- Writing to reset register 0x3 bit 2 '1' will reset this register's bits.

- Reading this register will clear it contents (recommended robust method) if configuration register #2 bit 4 is '1'.

- Writing to this register, write the bits just read assures clearing only bits that were handled. This also supports multiple interrupt services to work with a single register. This method is unique to Sital Technology Ips. Note that if interrupt causing bits are left high after write, an interrupt pulse will not be generated in pulse mode, but the interrupt line will stay active in level mode.

| Bit number | Read/Write/<br>default | Description                                                                                                                                                                                                                                                                                                                                                         |

|------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15         | Read                   | This bit is an OR of all interrupts bits of this register.                                                                                                                                                                                                                                                                                                          |

| 14         | Read                   | <ul> <li>'1' – RAM Parity Error detected. Requires Configuration register 2 bit 14 high, as<br/>well as Enhanced Mode, i.e., Configuration register 3 bit 15 high.</li> <li>This is an optional synthesis feature.</li> </ul>                                                                                                                                       |

| 13         | Read                   | '1' – Transmitter fail safe timeout. In the event that the BRM1553D transmits more<br>than 660 us it is not legal message, and there is a threat that the machines are<br>stuck. A separate circuit blocks this bus flooding after 768 us, and sets the bit high.<br>If set, this bit it is cleared only after receipt of a new valid command from the 1553<br>bus. |

| 12         | Read                   | '1' – Indicates that the RT command stack pointer has rolled over.                                                                                                                                                                                                                                                                                                  |

| 11         | Read                   | '1' – Indicates that the Monitor command stack has rolled over.                                                                                                                                                                                                                                                                                                     |

| 10         | Read                   | '1' – Indicates that the Monitor data stack has rolled over.                                                                                                                                                                                                                                                                                                        |

| 7          | Read                   | '1' – indicates RT Terminal Address Parity Error.                                                                                                                                                                                                                                                                                                                   |

| 6          | Read                   | '1' – indicates Time Tag Rollover from 0xFFFF to 0x0000.                                                                                                                                                                                                                                                                                                            |

| 5          | Read                   | '1' – When this bit is set high it indicates that the current RT message data in either circular buffer modes ( <u>local</u> or <u>Global</u> ) has rolled back to the buffer base. This bit is set only if <u>Config#2</u> , bit 1 is high.                                                                                                                        |

| 4          | Read                   | '1' – indicates an EOM occurred and the appropriate EOM bit was enabled in the control word.                                                                                                                                                                                                                                                                        |

| 2          | Read                   | '1' – Message Error has been detected OR transmitted data or status hasn't been echoed back correctly.                                                                                                                                                                                                                                                              |

| 1          | Read                   | '1' – Mode command has been received and it was enabled by its individual interrupt enable bit.                                                                                                                                                                                                                                                                     |